首页 >> 产品展示

产品展示--[计算机组成和体系结构开发实验平台]

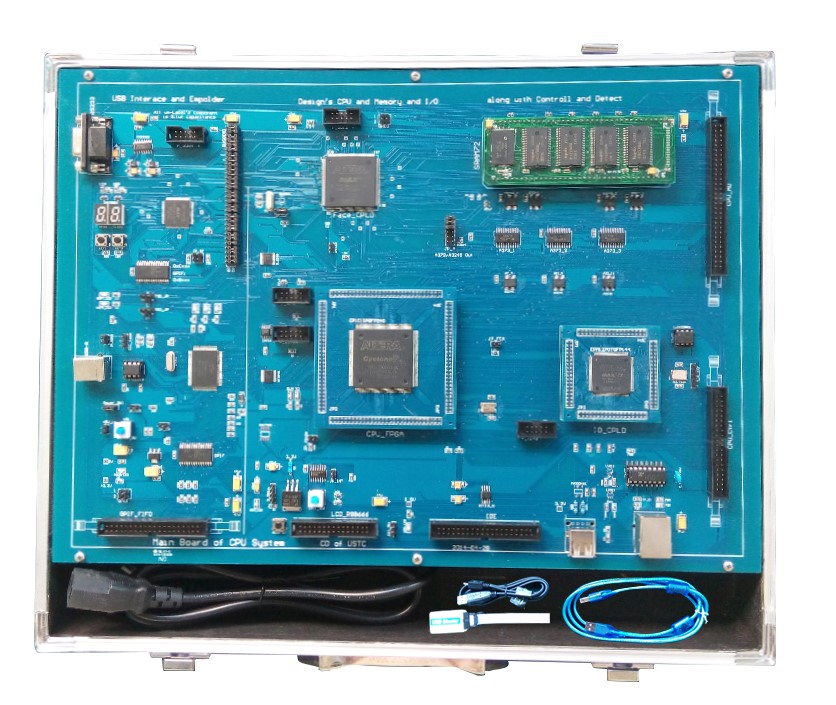

一、实验平台架构与特点 1、完全基于FPGA/CPLD的模块架构,结构支持USB的GPIF高速传送,组成如下: (1)USB设备开发与接口模块:包含USB核心器件CY7C68013(含8051内核)、串行EEPROM 24LC01B 、SRAM HY62WT081E、EPM3064ATC100、数据总线开关 SN74CB3Q3245、锁存器 74VHC373、方口USB接口。 (2)平台接口控制用CPLD模块:包含EPM3512AQC208主芯片、备频器DS1080L、JTAG下载接口等。 (3)CPU或IP Core用FPGA模块:包含核心器件EP1C12Q240C8、配置芯片EPCS4、JTAG下载接口等。 (4)主存模块4MB SRAM,由8片512K SRAM 62V8400A 组成,1MB Flash放BIOS或TOS,由AM29LA800BT组成。 (5)外围接口开发用CPLD模块:含EPM1270T144C4和JTAG下载接口等。 (6)CPU-BUS扩张模块:含USB双向差分器MAX3346E、SRAM HY62WT081E (7)以太网接口模块:含6PT8515、差分驱动器DS90LV011AH和差分接收器DS90LV012AH。 (8)串行通信接口:含MAX232电平转换器和RS232-9接口。 (9)GPIF接口:含SRAM HY62WT081E和IDC-40接口。 (10)自设计CPU外部接口:含TFT-LCD显示接口、IDE硬盘接口、LAN接口等。 2、结构灵活,便于扩充,适宜各种不同结构CPU和目标设计 (1)完全基于FPGA/CPLD的本身使其结构灵活 (2)用作CPU/IP Core的FPGA(30万门)和外围接口的CPLD使用背板转插,方便更换和维护。 (3)作CPU的FPGA设计了相当的备份信号并留有较多引脚连接。提供顶层调用目标的详尽描述模板和引脚配置文件。 (4)接口控制用CPLD(万门)模块逻辑描述开放,增改方便、说明详尽。 3、控制简单,操作方便,智能化的控制和检测功能 (1)带有上位主机的本系统调试debug(WIN2K/XP)软件,对CPU及其组成的实验计算机,具有启、停,程序加载与校验。 (2)在单步、单指、断点运行时,在CPU的跟踪回收逻辑配合下,debug将自动跟踪回收显示CPU内部寄存器、总线、状态等信息,可及时发现错误。用户可在CPU的跟踪回收逻辑里,自己选择所要看的信息。 (3)目标CPU可透明使用PC机的各种外部设备,在连续运行时可通过双机(主机与目标CPU)通讯(中断IO方式),输入实验计算机所需要的数据,显示运行数据、结果与状态。 (4) 对数字逻辑或其它系统实验(包括计算机组成原理与体系结构部件实验)时,用debug的读写存贮菜单,可对CPU/IP Core的FPGA的专用空间所设计的寄存器进行其输入数据和参数设置以及读出目标输出信息。 4、远程设计 1) 操作者可以通过网络的XP远程桌面进行设计实验,操作类同,效果一致。 二、实验课程项目 A、《计算机组成原理》与《CPU设计与测试》 (一) CPU各部件设计实验 1、译码器 2、简单指令部件(硬布线控制) 3、16位运算器 4、存贮器(用FPGA内SRAM) 5、FIFO先进先出存储器 6、8位累加器、双端口8×4累加器 7、16位电位型移位逻辑 8、8级嵌套堆栈 9、程序计数器 10、时序逻辑 11、3态总线等 (二)CPU设计实验 1、自定义8位指令系统CPU,指令形式:RISC、CISC、MISC; 2、16位指令8086/86兼容CPU,16-40条或全指令集; 3、MIPS的12-16条、32位简化兼容CPU。 (三) 创新CPU设计(配套提供教师讲课内容、实验文件PPT、学生作业内容和要求、设计参考等整套文档) 1、LC-3 结构CPU设计流程实验。 2、LC-3 结构并行流水设计实验。 B、《数字逻辑》 计数器、数码管译码电路、全加器、分频与系列波、4位数据汉明校验、简化串行通讯等。 C、《计算机体系结构》 1. 多CPU、共享存贮器、双机(M、S)通讯、浮点运算器等设计验证,外加CPU总线扩张板可做桥路、总线转换、存贮管理和控制部件、外设总体结构等实验。 2.外围设备接口逻辑设计实验包括IDE、TFT-LCD、LAN、USB、RS232、LPT等。 3.系统BIOS和TOS实验。 D、《硬件描述语言》与《高密度可编程器件应用》 VHDL、Verilog、AHD等语言编程设计、仿真与下载验证实验。 E、作为科研开发硬件逻辑或IP Core设计或USB设备开发的予验证和培训系统 1.所有实验目标的设计均使用硬件描述语言Verilog HDL和在系统可编程器件FPGA/CPLD实现。实验中学生不需要接任何线,专心于设计与验证调试。 2.实验过程:目标的Verilog HDL逻辑描述 → 编译通过 → 逻辑模拟仿真(手工、模板)验证 → 在实验平台测试下载目标逻辑和测试程序数据测试验证。 3.对FPGAD/CPLD编程下载提供顶层调用目标的详尽描述模板和引脚配置文件,为用户或设计者提供极大的方便。 4.如果是CPU设计、体系结构实验,其提高型还包括C语言编写的指令仿真机、汇编器或高级编译器设计,监控程序、BIOS、Tos操作系统设计(可与其它相关课程的实验配合进行)。 5.FPGA设计与编程使用Altera的MAX+PlusII10.2、QuartusII4.1-7.2系统。 三、实验箱配置表 序号 名称 说明 数量 1 实验主机箱 含详细技术指标里全部软硬件 1台 2 USB下载线 长1.5m 1根 3 方口USB通信线 长1.5m 1根 4 交流电源线1根 长1.5m 1根 5 短路片 30个 6 配套实验教材 (CPU设计与测试)(计算机原理与CPU设计实验指导) 1套 附:使用本实验箱需配套仪器仪表:万用表SHKC-WH12创新型计算机组成和体系结构开发实验平台

该产品被浏览1716次

相关产品